ユニバーサル入出力ICの開発

キーワード:ユニバーサル入出力(UIO),インターリーブA/D変換,出力モニタ機能,チッププラットフォーム

産業用コントローラなど信号入出力回路を有する機器において、設置場所に機器を導入したあとに、入出力対象を変更・追加することが考えられる。追加機器をできるだけ削減して、追加・変更に対応するためには、同じ端子を使って様々な入力対象および出力対象端子に対応できることが望ましい。さらに信号入出力回路を1つの構成で実現することによって、入出力ボードの種類を削減することが可能であり、在庫削減に貢献することができる。そこで、レジスタ設定により、同一端子で信号の入出力を可能とする、ユニバーサル入出力機能を有するチップ(以下、UIOチップ)を開発した。

1.はじめに

産業用コントローラは,石油化学プラント,鉄鋼,紙パルプなどのプラント産業,半導体,食品,自動車などの工場,ビル等の建物,上下水道,ガス,電気などの社会インフラの各分野における製造設備や制御機器に使用され,計測・制御システムの中核を担っている。これらは,流量計や圧力センサ,温度センサなどから入力したアナログ信号をデジタル信号に変換して読み込み,制御演算を行い,その結果に基づいて,制御信号を操作弁やシーケンス装置に出力することでプロセス制御を行っている。

いずれもA/D変換器,D/A変換器を含む入出力機能を有し,各種センサ・アクチュエータに対応する必要がある。各分野では,対象となるセンサ・アクチュエータが異なるものの,入力機能としては,電圧入力(0-10V,熱電対/零接点),電流入力(4-20mA),抵抗入力(3線,2線,ブリッジ),リレー接点,およびデジタル入力,出力機能としては,電圧出力(0-10V),電流出力(4-20mA),およびデジタル出力に集約される。製品ごとにI/O部を設計し,最適化されているが,共通部分が多く,プラットフォーム化することで,開発効率を上げることが望まれる。

この要望に対応するために,各種入出力機能を有する専用チップ(UIOチップ)を開発した。UIOチップを用いるとコントローラの各端子に対して,ソフトウェア切替えだけで各種入力機能,および出力機能を割り付けることが可能である。このユニバーサル入出力機能によって,いくつかの課題解決を実現できる。

まず,コントローラ機器導入後の構成変更を容易にする。コントローラの設置を行ったのち,センサ種の変更や入出力の拡張が必要になった場合,従来機器ではそれぞれの入出力に対応した基板や製品型番で構成されているため,コントローラ機器本体の交換追加が必要であった。この課題に対して, UIOチップ搭載のコントローラ製品では,ソフトウェアで内部レジスタの設定を変更することにより構成変更を行うことができる。

そしてお客さまの在庫管理コストも低減する。生産ラインなどの運用システムのダウンタイムを最小限にとどめるために,従来ではお客さまのもとでも入出力の種類ごとに在庫管理をする必要があり,管理コストも課題の1つとなっていた。UIOチップ搭載製品では製品型番を共通化することができ,ソフトウェアによって機能変更を設定できるため,お客さまの在庫品の種類を統一でき,在庫管理コスト削減につなげることが可能となる。

いちばんの特長であるユニバーサル入出力機能に加えて, UIOチップはコントローラの信頼性を確保するために,ほかにもいくつかの機能を搭載した。2章では機能概要,3章では回路構成について説明する。

2.機能概要

2.1 入出力切替機能

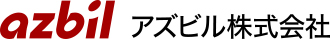

UIOチップは,最小限の外部素子(ディスクリート回路)を利用して,同じ外部端子で各種入力機能および出力機能をレジスタ設定で切り替えることができる,入出力切替機能を内蔵している(図1)。

図1 UIOチップ周辺ブロック

このように,設定の自由度を与えることによって次のような利点が考えられる。

- コントローラを設置場所に導入後,入出力対象が変更になった場合,または追加が発生した場合など,ソフト的な内部レジスタの設定変更により構成変更,および機能拡張を行うことができるため,対応した機器を追加する必要がない。

- 信号入出力回路を1つの構成で実現できるため,型番を共通化することができ,在庫削減に貢献することができる。

昨今のIoT時代に対応したシステム構築においては,短時間で検証結果を出し,システム改善サイクルを上げることが要求される。例えば温度センサとして安価なTCセンサを用いるシステム構築をしたのち,温度精度要求が強くなった場合でも,センサを測温抵抗体に取り換えることで,スピーディで柔軟なシステム構築が可能になる。ほかにも,あらかじめセンサ数や出力数が定まらないときでも,UIOチップ搭載のコントローラ機器は,入力種類の変更だけでなく,入出力自体も切り替えることができるため,システム変更に要する時間短縮が期待できる。

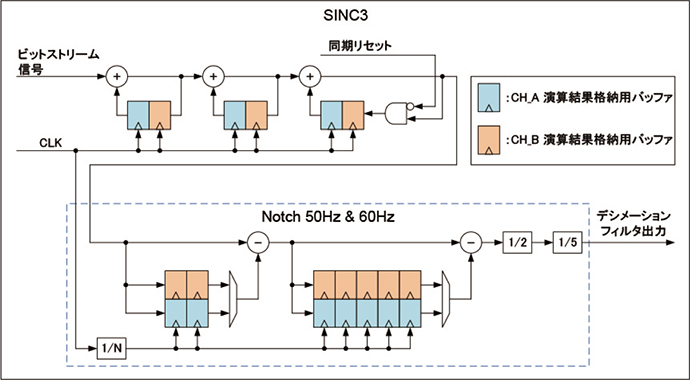

2.2 インターリーブΔΣA/D変換

UIOチップは,アナログ信号用のA/D変換用に,2チャンネルの2次ΔΣ型A/D変換回路を内蔵している。独自開発したΔΣ型A/D変換回路は,1つの回路ブロックで2チャンネルの変換に対応するために,アナログ信号のサンプリングの動作からデシメーションフィルタによる量子化ノイズ除去までを,2チャンネル交互にサンプリングを行うインターリーブ式を採用したことを特長としている。

1つの回路で2チャンネルの入力に対応するためには,マルチプレクサを用いて入力信号を切り替える方式が一般的であるが,入力信号を切り替えるたびにΔΣ型A/D変換器を構成する積分回路やデシメーションフィルタをリセットする必要がある。2次ΔΣA/D変換回路は,量子化ノイズ除去に3次の特性のフィルタを使用するため,フィルタリセット直後のデータ出力に出力レート3周期分の処理レイテンシが発生する。高精度計測が求められるなか,ΔΣ型A/D変換器は非常に有望であるが,その一方で制御周期を短くしたいという市場要求に対しては,大きな課題となっていた。開発したUIOチップに搭載した独自のA/D変換回路によって,この相反する要求を実現させた。

2.3 商用ノイズ抑制フィルタ機能

コントローラ機器が設置される環境はモータや様々な機器が動作している環境であり,商用電源周波数に同期した大きなノイズがまん延している。周知のように日本国内だけでも50Hzと60Hzが地域によって使用されており,商用電源周波数のノイズを抑制するためには,両方の周波数での除去特性を有する必要がある。最も簡単で従来から採られる手段は,時定数の大きなフィルタによって除去する方法である。しかし時定数が大きいフィルタによって,高速の信号変化を捉えることは当然できない。

上述の矛盾する要求を答えるため,高速動作が可能な商用ノイズ抑制フィルタも独自開発した。

2.4 出力モニタ機能

UIOチップは,同一端子を入力端子および出力端子に使用できるように,チャンネルごとのA/D変換器とD/A変換器が搭載されている。そのため,出力設定時に,内蔵のA/D変換器を用いて出力端子の監視を行うことで,断線,短絡,および誤接続による異常を検知することができる。

電圧出力の場合は,出力端子の基準電圧からの電位差,電流出力の場合は,検出抵抗に生じる基準電圧からの電位差を,それぞれ電圧入力としてA/D変換することで,負荷接続点の出力値を検出する出力モニタ機能を搭載した。例えば,電流出力時に断線が起こった場合,検出抵抗に電流が流れないため,モニタされたA/D変換値が設定値と大きく異なる値になる。これにより,異常を検知することができる。

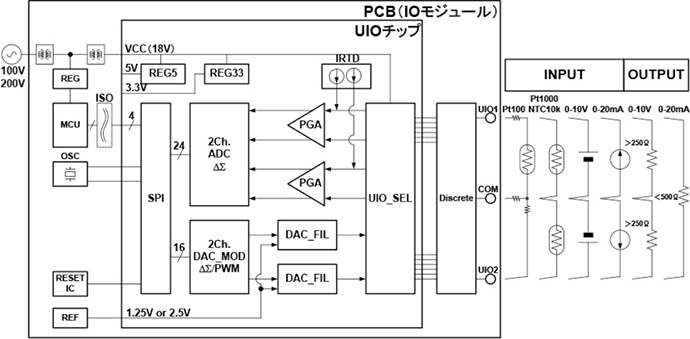

2.5 高信頼性読み出し機能

UIOチップは,MCU(Microcontroller)等の制御デバイスとの接続バスとしてSPI(Serial Peripheral Interface)を採用している。UIOチップは,このSPI経由でのA/D変換結果の送信時に連番のIDを付加し,MCU等の制御デバイスは,このIDを用いてA/D変換結果の更新およびデータ欠損の判定を行うことができる。UIOチップは,MCUからどのようなタイミングでA/D変換読み出し要求を受け取ったとしても変換結果が破壊されないよう保護するため,MCUは任意のタイミングで更新判定が可能である。また,産業用途では読み出しデータの信頼性も求められるため,UIOチップはSPI通信時のCRC(Cyclic Redundancy Check)またはチェックサム付加にも対応している。さらに,A/D変換結果をチャンネルごとに最大1024回,二乗和を行う機能を内蔵しており,MCUが電力の実行値計算をする際の負荷を低減することができる。この二乗和はUIOチップから出力可能な制御信号オン時の積算値,オフ時の積算値,オン/オフの区別をしない積算値の計3通りの算出が可能であり,オン/オフ切り替えによる過渡応答中の期間の積算を除外することもできるため,図2のようにヒータ等の制御における短絡検出,断線検出に応用することができる。

図2 ヒータ制御における短絡・断線検出

3.回路構成

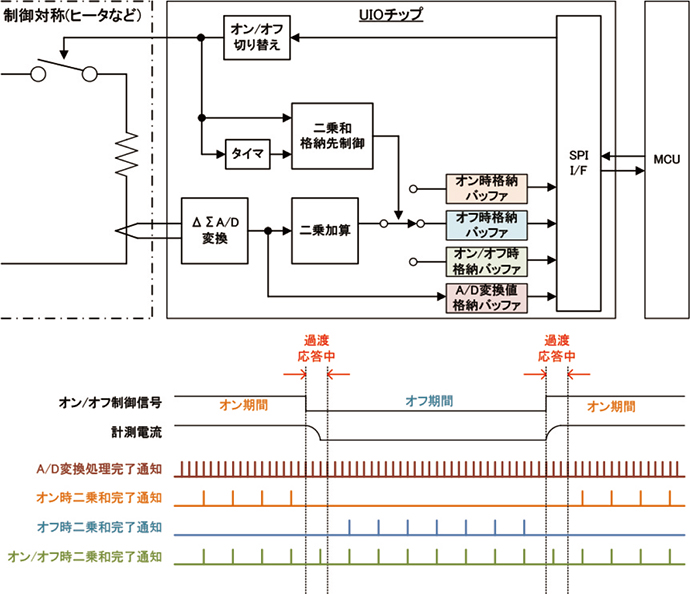

図3に示すように,UIOチップは,入出力切替部,PGA (プログラマブル・ゲイン・アンプ),抵抗センサ用励起電流源,および2チャンネル2次ΔΣ型A/D変換回路を含む入力回路,D/A変換回路を含む出力回路,SPI通信回路,レギュレータ回路を搭載する。各ブロックの回路構成について説明する。

図3 UIOチップブロック図

3.1 入出力切替部

同一の外部端子を使って入出力機能を実現する。そのためには,外部端子の入力インピーダンスをHigh-Zにする構成を必要とする。具体的には,電流入力検出抵抗,電圧出力分圧抵抗,電流出力検出抵抗,および抵抗センサ用参照電圧検出抵抗の電流パスを切り離す構成である。入出力対象切替回路の状態は,インターフェース回路を介してソフトウェアにより設定することができる(表1)。

表1 入出力レジスタ設定

| NO. | チャンネル1 | チャンネル2 | |

|---|---|---|---|

| 入力選択 | 出力選択 | 選択可能な入出力 | |

| 1 | ─ | ─ | ─ |

| 2 | 3線RTD① | ─ | ─ |

| 3 | 2線RTD | ─ | ①②除くすべて |

| 4 | サーミスタ | ─ | ①②除くすべて |

| 5 | 熱電対 | ─ | ①②除くすべて |

| 6 | 冷接点 | ─ | ①②除くすべて |

| 7 | ブリッジ抵抗 | ─ | ①②除くすべて |

| 8 | 電圧入力 | ─ | ①②除くすべて |

| 9 | 電流入力 | ─ | ①②除くすべて |

| 10 | ─ | 電圧出力 | ①②除くすべて |

| 11 | ─ | 電流出力② | ─ |

| 12 | 入力校正 | ─ | ① 除くすべて |

この入出力切替部では,チップ端子数および外部素子を最小限にするように設計を行った。様々な入力素子,出力負荷が接続されるため,耐圧,過電流,ESD/LU,および誤接続に対する対策を行った。

3.2 入力切替回路

UIOチップの入力回路は,0-10V電圧入力,4-20mA電流入力,測温抵抗体(RTD),熱電対(TC)など,各種入力信号に対応した選択機能を持ち,選択した入力に対してノイズのフィルタリングと増幅を行い,後段のA/D変換回路に信号を入力する。入力回路は,外部端子の接続状態を切り替える選択回路と,ノイズ除去用のローパスフィルタ回路,電圧増幅およびバッファ用のPGA(プログラマブル・ゲイン・アンプ)回路,ΔΣ型A/D変換回路で構成されている。また,RTD (測温抵抗体)の励起用に,定電流源回路も内蔵している。

選択回路は,スイッチと誤接続保護用の抵抗で構成されている。内部レジスタ設定に従って,外部端子とPGA回路間のパスを切り替えることで,基板の部品実装を変えることなく,様々な系統の信号入力に対応できる。

3.3 定電流源回路

定電流源回路は,出力電流を50uA~1mAの範囲で設定でき,3線式RTDの励起用に最大2系統の出力が可能である。2系統出力時のマッチングを高めるために,電流パスを交互に入れ替えることで,相対誤差の軽減を実現している。

3.4 フィルタおよびPGA回路

アナログ入力信号は内蔵のローパスフィルタ回路によってノイズを除去する。このフィルタ回路は,キャパシタとチップ内蔵のポリ抵抗とで構成されるパッシブフィルタである。ポリ抵抗の抵抗値は,選択回路の設定にかかわらず一定となるよう調整されており,キャパシタの容量値で時定数を選択する。

PGA回路は,2つのチョッパー安定化アンプと,PGAのゲインを設定する抵抗帰還ネットワークで構成されている。チョッパー安定化アンプを採用しているため,低ドリフト(低オフセット)を実現する構造となっている。PGAの増幅率は1倍~128倍まで設定できる。

3.5 A/D変換回路

A/D変換回路は,前述のインターリーブΔΣ型A/D変換回路である。最大2チャンネルのアナログ信号のA/D変換に対応し,データレートを100SPS~1600SPSの範囲で設定可能である。A/D変換回路は,スイッチトキャパシタ式積分回路を用いたΔΣ変調回路と,量子化ノイズ除去のためのデシメーションフィルタで構成される。多くの回路素子を共有することで,A/D変換回路を2個搭載する場合と比較して,回路面積を削減している。

3.6 商用ノイズ抑制デシメーションフィルタ

UIOチップのΔΣA/D変換は,インターリーブ式のΔΣA/D変換であるため,量子化ノイズ除去のためのデシメーションフィルタを2つのチャンネル間で共用することが可能となる。さらに,商用ノイズ(50/60Hz)除去のためのデジタルフィルタの伝達関数とデシメーションフィルタの伝達関数を見直し,最適化することで,2つのフィルタを単純に直列接続した場合と比較して面積を約40%削減することができた。この最適化されたデシメーションフィルタは,量子化ノイズの除去に加えて,商用ノイズをおよそ55dB減衰することができ,チャンネル切り替え時の高速応答も可能である(図4)(1)(2) 。

図4 商用ノイズ抑制デシメーションフィルタ

3.7 出力回路

電流出力,電圧出力に用いる変調信号は,ゼロ出力時の精度とリップル精度の要求に対応するために,特殊PWM信号(16ビット,8ビット分割型,1MHz),とΔΣ型変調信号(16ビット,100kHz)のどちらを使うかをレジスタ設定により選択することができる。

変調信号の平滑化に用いるローパスフィルタは,内蔵の100kΩ抵抗と外部キャパシタによるRCフィルタの構成をとっており,キャパシタの容量により時定数を選択することができる。例えば,33nFの外付けキャパシタと組み合わせた場合,63%応答の時間が約10msecとなる。

平滑後の増幅回路はゲイン設定機能を含み,外付け回路との組合わせにより,0-10Vや0-5Vなどの電圧出力, 4-20mAの電流出力が可能である。UIOチップには,独立した2チャンネルの出力回路が搭載されており,電圧出力においては,異なる値に設定した2チャンネルの同時出力が可能である。電流出力においては,1チャンネル出力となる。

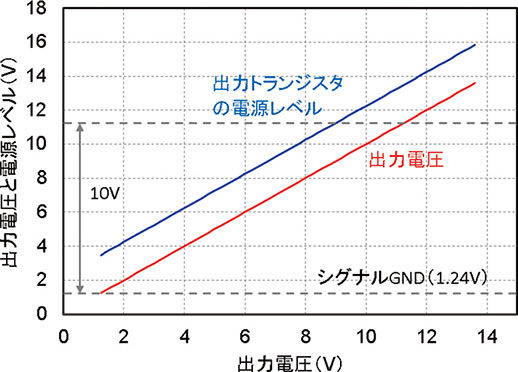

3.8 プレレギュレータ

電圧出力,電流出力において,発熱を抑えるプレレギュレータ回路を搭載した。この回路によって外付け駆動トランジスタの電源電圧を出力値に応じて制御して,駆動トランジスタのコレクタ-エミッタ間,またはドレイン-ソース間の電圧を下げることで,発熱を抑えることが可能になる。プリレギュレータ回路は,外部の降圧型スイッチング電源と接続する。出力値をモニタして,駆動トランジスタの電源電圧を基準とした三角波と比較を行い,スイッチング電源のPWM制御信号を出力する。三角波はロジック回路から100kHzを入力し,容量(100pF)への充放電を用いて生成する。図5に出力電圧と出力トランジスタの電源レベルを示す。ドレイン-ソース間電圧をおよそ2.24V程度固定することができる。

図5 プリレギュレータ機能(測定値)

3.9 SPI通信部

UIOチップのSPI通信部は,MCUからアクセスタイプ設定コマンドを受け付けることにより,SPIアクセスを通常アクセス(チェックサム,CRCともに付加なし),チェックサム付加アクセス,CRC付加アクセスの3通りから選択することができる。UIOチップが付加するCRCの生成多項式は,多くのMCUでハードウェア演算が可能なCRC16-CCITTを用いているため,CRC算出ハードウェアを内蔵するMCUであれば演算負荷を増やすことなく,SPIアクセスの信頼性を高めることが可能である。CRC算出ハードウェアを持たないMCUを用いた製品に対してUIOチップを適用する場合は,CRCではなくチェックサムを付加したアクセスにすることで,演算負荷を抑え,SPIアクセスの信頼性を高めることができる(表2)。

表2 SPIアクセスタイプ

| 通常アクセス | チェックサム付加 | CRC付加 | ||

|---|---|---|---|---|

| 演算負荷 | ◎ | 〇 | △※ | |

| アクセス時間 | ◎ | 〇 | △ | |

| 信頼性 | △ | 〇 | ◎ |

※ MCUがCRC算出ハードウェアを内蔵する場合は◎

4.評価結果

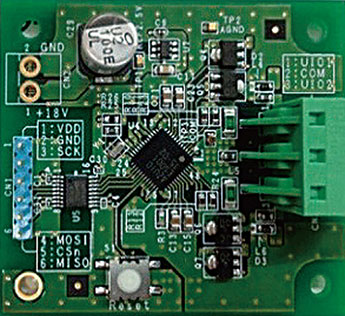

1章で説明したように,UIOチップは入出力回路のプラットフォーム化を目的の1つとしている。このため,対象となる現行製品の仕様から,今後の製品搭載にあたりチップの満たすべき特性を決め,設計を行った。チップ評価から,これらの特性が基本的に達成されていることが確認できた。

評価基板(中央にUIOチップ)

また,UIOチップでは,ESD試験や高温連続動作試験などのICにおける一般的な信頼性試験項目のほかに,計測制御の専業メーカならでの視点で,製品に搭載された場合の特定アプリケーションにおける耐量試験も併せて行っている。例えば,計装時,無電源状態で電圧入力を逆接続で受けるといったような想定できる不注意に対しても,故障が生じないように,市販ICでは行わないような耐量試験も実施してアズビル製品の信頼性を高めている。

5. おわりに

コントローラ製品のアナログ・デジタルI/O機能プラットフォームとして,ユニバーサル入出力IC(UIOチップ)を開発した。UIOチップは,コントローラ製品に必要なほぼすべての入出力種別に対して,少ない外付け部品だけでI/O構成が可能である。構成切り替えは内部レジスタによる切り替え設定で行うことができる。また,インターリーブΔΣ A/D変換回路の採用により,チャネル間の同時性を確保でき,高速に商用電源ノイズ除去を可能とした。

<参考文献>

(1) H. Kuribayashi and T. Kajita, “Area-Efficien Decimation Filter with Power-Line Noise Suppression for ΔΣ A/D Converters” SICE Annual Conference 2016

(2) H. Kuribayashi and T. Kajita, “Area-Efficie Decimation Filter with 50/60 Hz Power-Line Noise Suppression for ΔΣ A/D Converters” SICE Journal of Control, Measurement, and System Integration Vol.10 (2017) No.3 p.165-169

<著者所属>

加藤 太一郎 アズビル株式会社 技術開発本部センシングデバイス部

栗林 英毅 アズビル株式会社 技術開発本部センシングデバイス部

手島 紘昭 アズビル株式会社 技術開発本部センシングデバイス部

小木曽 康弘 アズビル株式会社 技術開発本部センシングデバイス部

梶田 徹矢 アズビル株式会社 技術開発本部センシングデバイス部

平山 博文 アズビル株式会社 アドバンスオートメーションカンパニー CP開発部

井波 太郎 アズビル株式会社 ビルシステムカンパニー開発本部開発4部

この記事は、技術報告書「azbil Technical Review」の2018年04月に掲載されたものです。

- 2024

- 2023

- 2022

- 2021

- 2020

- 2019

- 2018

- 巻頭言:「人を中心とした」の発想に基づく人とシステムとの共創

- 特集に寄せて:競争力あるアズビルならではの生産体制機構に向けて─人と機械・システムとの協調を通じた生産変革─

- 熱源システム運転の効率化に貢献するクラウドサービスの開発

- オペレータの意思決定を支援するバッチプロセス向けオンライン異常予兆検知手法の開発

- 都市ガス事業者の地震対策を支援するガバナ監視システムの開発

- 居住者に「快適」を提供する温冷感リクエスト型空調の開発

- 熱伝導率の温度特性を利用した天然ガス計測技術の開発

- ユニバーサル入出力ICの開発

- 13 Paレンジサファイア隔膜真空計の開発

- 感度波長拡大型UVチューブの開発

- ディマンドリスポンスシステムの開発とバーチャルパワープラント構築実証事業への適用

- IoT時代の熱源コントロール・ソリューションの紹介

- 2017

- 2016

- 2015

- 2014

- 2013

- 2012

- 2011

- 2009

- 2008

- 2007

- 2006